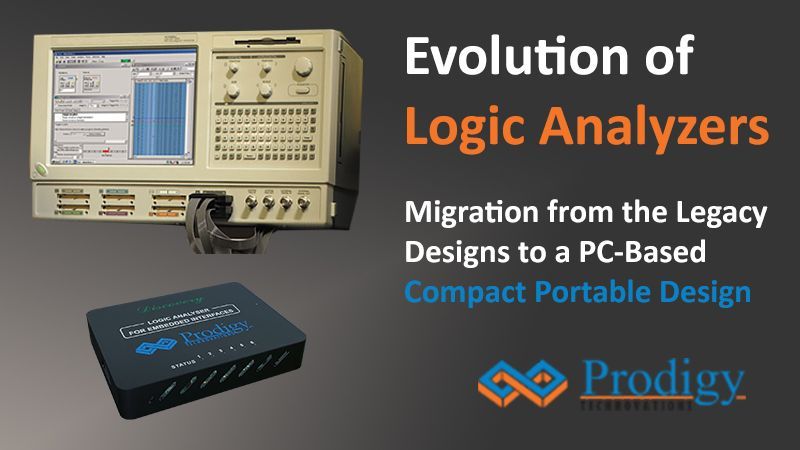

Evolution of Logic Analyzers

Evolution of Logic Analyzers: Future of Logic Analyzers in embedded system design

Traditionally Logic Analyzers are used to monitor parallel buses in microprocessors, microcontrollers, or PATA or memory interface-based designs. Data transfer between microprocessor and peripherals ICs is using the parallel bus. Programming of microprocessors or microcontrollers used to be in assembly language. To support debug digital design Logic Analyzers provided 100s of channels, advanced parallel pattern triggers, long acquisition memory, and disassemblers for different microprocessors and microcontrollers. Disassembler is additional hardware commonly called ‘PODS’ used to capture the data in microprocessor/microcontrollers IOs. Software associated with the POD is used to disassemble the captured data and display it in assembly language. This runtime assembly language code is used to provide great details enabling designers to debug and optimize the designs.

But modern electronics designs moved away from parallel bus design for good and adapted serial bus architecture for low-speed, high, and ultra-high-speed designs. Current digital designs are based on a system on a chip that has multiple low-speed and high-speed serial bus interfaces to support different design needs. Data transfer between ICs or peripherals takes place using protocol using the serial bus. Product differentiation is driven by software features which continuously updated to add more capabilities. This has driven demand for a different set of capabilities in Logic Analyzer. To support these design needs Logic Analyzer does not need to be a high channel count but it should be capable of capturing data from multiple serial bus designs and displaying it in a time-correlated form so that designers can visualize the system-level operation. But just viewing the digital waveforms it is extremely difficult to interpret the serial data. Hence Logic Analyzer should provide multiple serial bus decoding capabilities. This simplifies the entire debug process.

Debugging any design is a very challenging activity. Designers need to find the root cause using the symptoms such as bus failure, boot failure, etc. Designers try to narrow down by eliminating different possible causes of the symptoms by looking at specific data and analyzing them. To get to the specific cause, the Logic analyzer should have the capability to define triggers on specific events or the ability to look for multiple events and take smart actions so that the root cause of the systems can be found.

This New generation Logic Analyzer supports the following capabilities.

- Good enough channel count (could be 10 to 32)

- Serial bus data analysis for different Protocols

- Simultaneously decode multiple Protocols

- Protocol-aware trigger capabilities

- Long acquisition support with pre and post-trigger capabilities

Prodigy Technovations offers Logic Analyzer to debug design in embedded system design. The logic analyzer is equipped to handle complex engineering problems.