UFS 4.0 Protocol Analyzer

Product

Overview

Datasheet

Presentation

Application

Notes

PGY-UFS4.0-PA, UFS Protocol Analyzer is the industry-first working and tested UFS4.0 Protocol Analyzer. It offers protocol data capture and debugging of data across MPHY, UniPro, and UFS protocol layers. It allows for instantaneous decoding of UFS, UniPro, and MPHY layers with the flexibility to correlate decoded data across these protocol layers. PGY-UFS4.0-PA supports PWMG1 to HSG5B data rates and two TX, and two RX lane decode. The active probe has minimum electrical loading on the device under test (DUT) and captures protocol data without affecting the performance of DUT. PGY-UFS4.0- PA Protocol Analyzer supports two-lane data. Comprehensive on the fly decoding of UniPro & UFS data enables validation of communication between UFS host and device.

PGY-UFS4.0-PA Protocol Analyzer allows Design and Test Engineers to obtain deep insight into UFS host and device communication. MPHY/UniPRO/UFS packet-based triggering allows specific protocol data capture and analysis. PGY-UFS Protocol analyzer instantaneously provides decoding of UFS, UniPro, and MPHY layers with a correlation to MPHY, UniPro, and UFS layers.

JTAG Protocol Exerciser and Analyzer Datasheet

Key features

- Supports JTAG frequencies of up to 25MH

- Simultaneously generate JTAG traffic and Protocol decode of the Bus

- JTAG Master Capability

- Variable JTAG Data speeds and Duty cycle

- User-defined TCK & TDI Delays

- Continuous streaming of protocol data to the host computer to provide a large buffer

- A timing diagram of Protocol decoded bus

- Listing view of Protocol activity

- Error Analysis in Protocol Decode

- Ability to write exerciser script to combine multiple data frame generation at different data speeds

- USB 2.0/3.0 host computer interface

- API support for automation in Python or C++

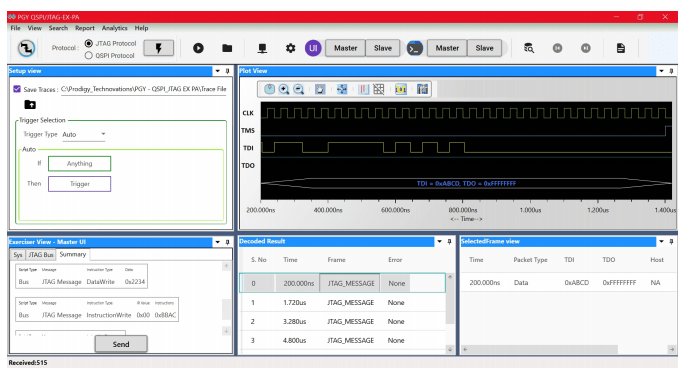

Multi-Domain View

Multidomain View provides the complete view of JTAG Protocol activity in a single GUI. Users can easily set up the analyzer to generate JTAG traffic using a GUI or script. Users can capture JTAG Protocol activity at a specific event and decode the transition on the JTAG bus. The decoded results can be viewed in the timing diagram and Protocol listing window with autocorrelation. This comprehensive view of information makes it the industry’s best, offering an easy-to-use solution to debug the JTAG protocol activity.

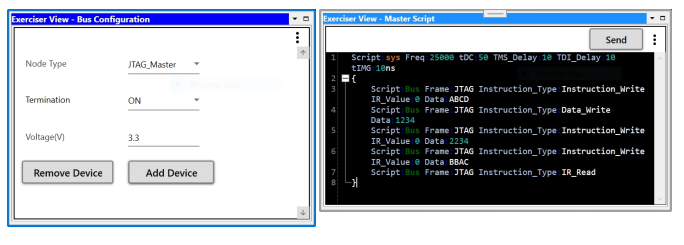

Exerciser

PGY-JTAG-EX-PD supports JTAG traffic generation using GUI and Script. Users can generate simple traffic generation using the GUI to test the DUT. Script-based GUI provides flexibility to emulate the complete expected traffic in the real world including error injections. In this sample script user can generate JTAG traffic as below:

Script Line #1: Set system Frequency 25MHz, Duty cycle to 50%, set TMS_Delay to 10ns, set TDI_Delay to 10 ns, and set inter message gap t0 10ns. Script Line #3: Instruction_Write

Script Line #4: Data_Write

Script Line #5: Instruction_Write

Script Line #6: Instruction_Write

Script Line #7: IR_Read

Timing Diagram and Protocol Listing View

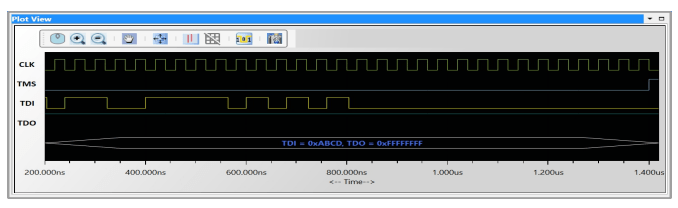

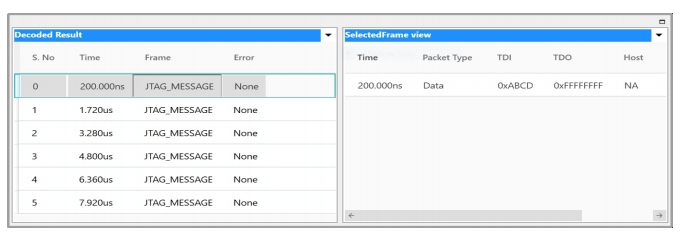

The timing view provides the plot of CLK, TMS, TDI, and TDO signals with a bus diagram. Overlaying of Protocol bits on the digital timing waveform will help easy debugging of Protocol decoded data. Cursor and Zoom features will make it convenient to analyze Protocol in the timing diagram for any timing errors.

The protocol window provides the decoded packet information in each state and all packet details with error info in the packet. The selected frame in the Protocol listing window will be autocorrelated in the timing view to view the timing information of the protocol window and provides the decoded packet information in each state and all packet details with error info in a packet. The selected frame in the Protocol listing window will be autocorrelated in the timing view to view the timing information of the packet.

Key Specifications

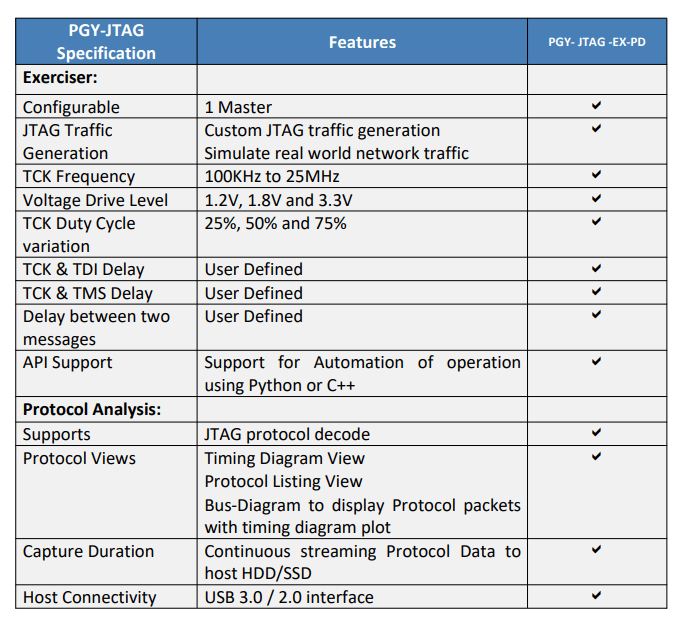

JTAG Specifications