UFS 4.0 Protocol Analyzer

Product

Overview

Datasheet

Presentation

Application

Notes

PGY-UFS4.0-PA, UFS Protocol Analyzer is the industry-first working and tested UFS4.0 Protocol Analyzer. It offers protocol data capture and debugging of data across MPHY, UniPro, and UFS protocol layers. It allows for instantaneous decoding of UFS, UniPro, and MPHY layers with the flexibility to correlate decoded data across these protocol layers. PGY-UFS4.0-PA supports PWMG1 to HSG5B data rates and two TX, and two RX lane decode. The active probe has minimum electrical loading on the device under test (DUT) and captures protocol data without affecting the performance of DUT. PGY-UFS4.0- PA Protocol Analyzer supports two-lane data. Comprehensive on the fly decoding of UniPro & UFS data enables validation of communication between UFS host and device.

PGY-UFS4.0-PA Protocol Analyzer allows Design and Test Engineers to obtain deep insight into UFS host and device communication. MPHY/UniPRO/UFS packet-based triggering allows specific protocol data capture and analysis. PGY-UFS Protocol analyzer instantaneously provides decoding of UFS, UniPro, and MPHY layers with a correlation to MPHY, UniPro, and UFS layers.

SD/SDIO UHS-II Protocol Analyzer Datasheet

Key features

- Continuous monitoring and streaming of protocol data to capture elusive events (more than 30GB data capture)

- Protocol tests of captured data for protocol integrity, DCMD, CCMD, MSG, and DATA

- Instantaneous display of Protocol activity while the PGY-UHS-II is capturing the Protocol data allowing almost live analysis of protocol activity

- Hardware-based protocol-aware trigger capability enables capturing specific events

- Trigger on CRC error conditions allows capturing infrequent error events

- Users can identify the anomalies by decoding the command and response argument

- Analytics provides analysis of acquired protocol data by plotting command, response, data, and frequency of operation over acquired time

- Decoding of device registers for easy analysis

- The filter feature allows you to view specific packets in decoded protocol packets

- Search for specific events in protocol activity

- Easy-to-use software user interfaces reduces the learning curve of protocol analysis

- Software is designed to handle long-duration capture and display of the decoded data without demanding extensive resources in the host computer

- Insertion of markers in protocol activity helps in correlating the input digital signal with Protocol Activity

- Trigger out a signal for any specific protocol event allows the triggering of other instruments such as an oscilloscope

- Interface to host system using USB3.0 or Gigabit Ethernet interface

- Flexibility to upgrade the hardware firmware using the GbE interface provides easy field up-gradation of firmware

- Decoded data packets can be exported to CSV file for further analysis

PGY-UHS-II SD/SDIO UHS-II Protocol Analyzer is the most feature-rich comprehensive Protocol Analyzer available to capture and debug UHS-II protocol data. PGY-UHS-II Protocol Analyzer supports FD156 and HD312 data rates. The innovative active probe has minimum electrical loading on the device under test (DUT) and captures protocol data without affecting the performance of the DUT. PGY-UHS-II protocol analyzer allows streaming of protocol data from PGY-UHS-II Protocol Analyzer to the host system (using USB 3.0 or GbE interface). Comprehensive decoding of data, protocol tests, and error analysis enables verification of the communication between the UHS-II host and device.

PGY-UHS-II Protocol Analyzer allows Design and Test Engineers to test and debug SD UHS-II Interface triggering on command, response, data, or CRC errors. PGY-UHS-II Protocol analyzer instantaneously provides decoding of CCMD, DCMD, MSG, DATA, and its arguments. The Analytics feature offers a graphical representation of command, response, data, and frequency of operation for the acquired duration.

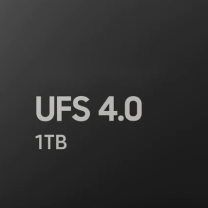

Specifications

Interfaces Supported | SD4.0 (UHS-II), FD156 and HD312, SDIO |

Protocol Decode | CCMD, DCMD, MSG, DATA, Arguments, Device registers |

Data Decode | Supported |

Protocol Test | Protocol Integrity, CRC Errors, Timing values, Data CRC Errors, Reserved commands |

Storage Capability | Continuous streaming of protocol activity up to 30GB |

Capture Mode | Manual Run/Stop, Time-specific |

Trigger on | DCMD. CCMD, MSG, SYN, BSYN, DIR, LIDL DID, SDB. SOP, EOP EDB |

Trigger Actions | Capture data and/or trigger out signal |

Host Machine Minimum Requirements | Microsoft Windows 8, Windows 7, 16GB of RAM; Storage with at least 50 GB HDD space for the storing the acquired cata: Display with resolution of at least 1024×768 |

Setup

PGY-UHS-II Protocol Analyzer provides USB3.0 and GBe interface for host connectivity. PGY-UHS-II software runs in the host machine enabling the configuration of PGY-UHS-II hardware for UHS-II protocol analysis storage.

UHS-II Interposers

Prodigy Technovations provides UHS-II fixture /interposer. This allows users to probe UHS-II Signals to monitor the protocol between host and device.

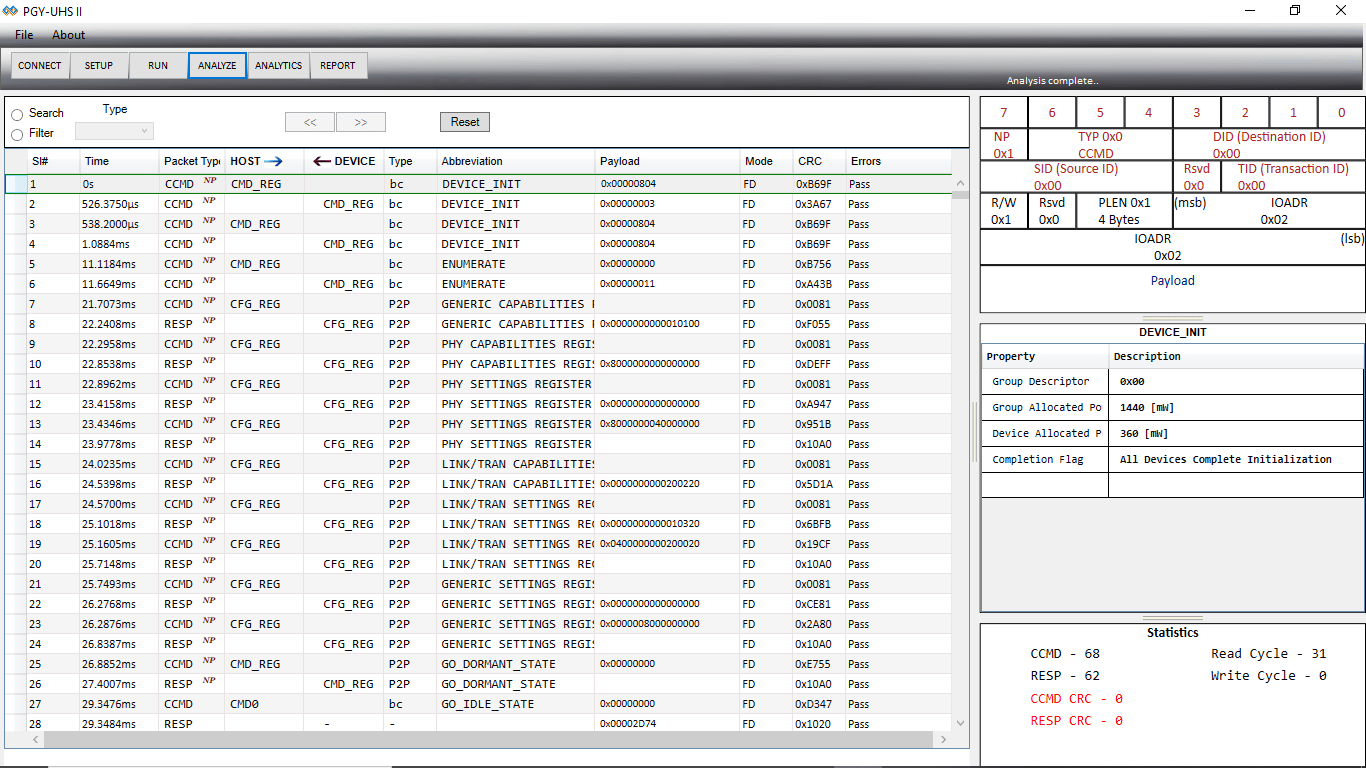

Comprehensive Protocol Analysis

PGY–UHS-II Software provides the industry’s best protocol analysis capabilities. Easy to use interface reduces the protocol analysis time. Time-stamped view of protocol decode listing provides an easy view of protocol activities between host and device. At the click of a button, the user can get a decode of the argument of Response from the device. Decoding of registers provides detailed information on devices. Analytics features quickly provide insight into protocol activity without going through the complete protocol activity.

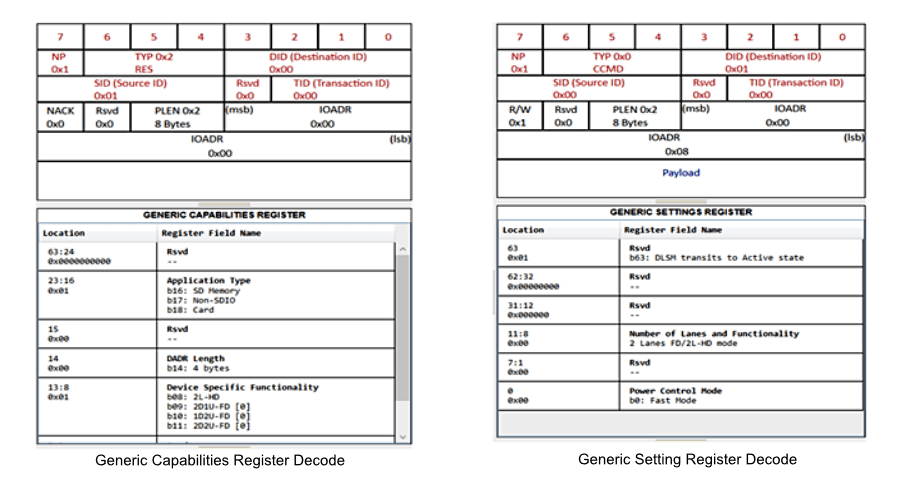

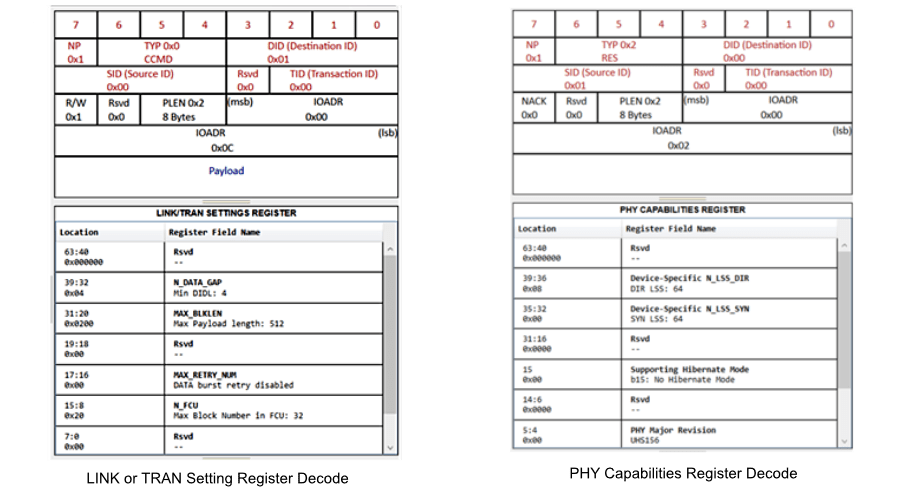

Powerful Decode capabilities Registers

PGY-UHS-II Protocol Analyzer quickly decodes the UHS-II register and displays the register filter name. These decode tables allow identity the host and device setting being set and quickly debug it. The above image displays the Generic capabilities and settings between the host and the device.

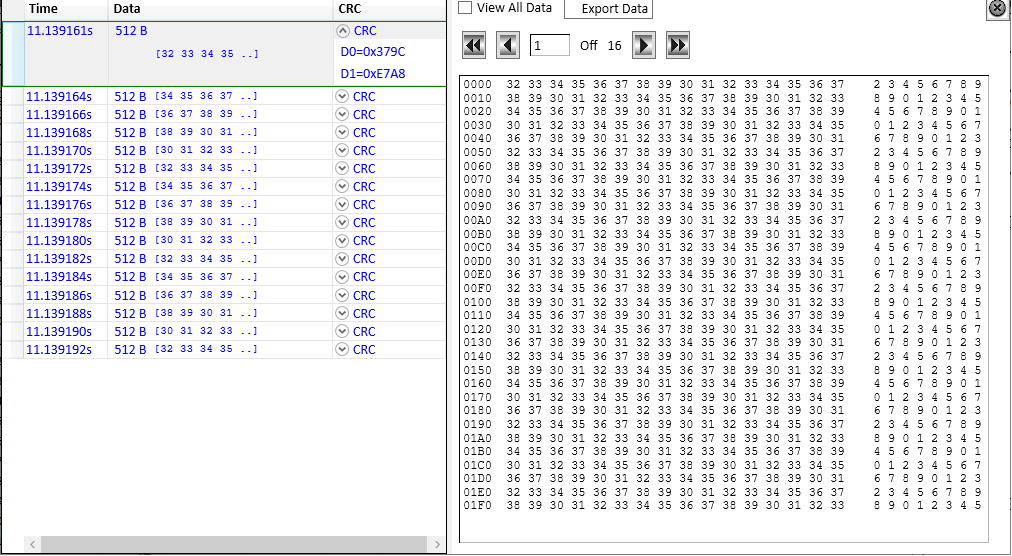

Data Packet Analysis

PGY-UHS-II automatically identified if the data transfer is FD156 and HD512 mode. PGY-UHS-II will decode data commands and identifies, if data is in HD and FD mode, and captures data. The display of captures can be viewed for each command. The data block is displayed below:

The software will validate CRC values and highlight them in red color, for any CRC failure. Data is displayed in HEX and ASCII format for each block.

Analytics

PGY-UHS-II offers analytical feature displays time-stamped packets of the host, device, and data exchange in a time domain view. This allows the user to look at protocol activity traffic between the host and the device.

Users can export the Protocol decoded to a Txt file for documentation and further analysis in a user environment.

Key Specifications