UFS 4.0 Protocol Analyzer

Product

Overview

Datasheet

Presentation

Application

Notes

PGY-UFS4.0-PA, UFS Protocol Analyzer is the industry-first working and tested UFS4.0 Protocol Analyzer. It offers protocol data capture and debugging of data across MPHY, UniPro, and UFS protocol layers. It allows for instantaneous decoding of UFS, UniPro, and MPHY layers with the flexibility to correlate decoded data across these protocol layers. PGY-UFS4.0-PA supports PWMG1 to HSG5B data rates and two TX, and two RX lane decode. The active probe has minimum electrical loading on the device under test (DUT) and captures protocol data without affecting the performance of DUT. PGY-UFS4.0- PA Protocol Analyzer supports two-lane data. Comprehensive on the fly decoding of UniPro & UFS data enables validation of communication between UFS host and device.

PGY-UFS4.0-PA Protocol Analyzer allows Design and Test Engineers to obtain deep insight into UFS host and device communication. MPHY/UniPRO/UFS packet-based triggering allows specific protocol data capture and analysis. PGY-UFS Protocol analyzer instantaneously provides decoding of UFS, UniPro, and MPHY layers with a correlation to MPHY, UniPro, and UFS layers.

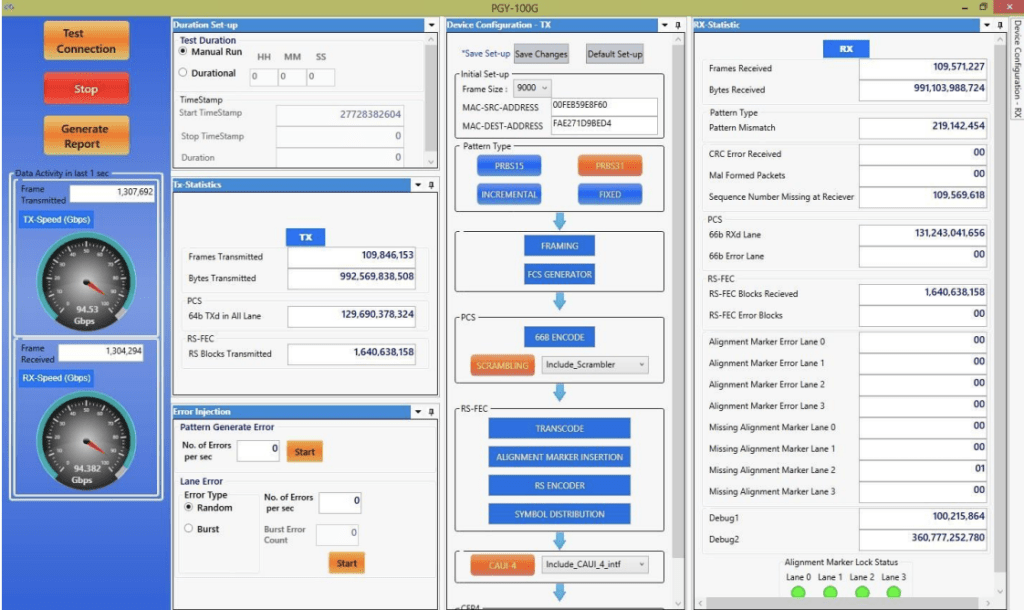

100G 802.3_2015 BERT and Analyzer Datasheet

Key features

Fully Compliant to IEEE802.3bm – 2015 Standard

● Flexibility to transmit Fixed, PRBS, and Incremental pattern

● Reed Solomon Encoder, Decoder as per standard

● Random and Burst Error injection. The error rate is programmable

● Error injection in RS Layer and PCS after RS encoder

● Transmit and Receive Statistics include RMON and extensive error counts

● Option to bypass scrambling, RS encoder

● Real-time Transmitter and Receiver throughput display with a programmable frame rate

● Fixed frame sizes from 64 bytes to 9600 bytes or Random Size.

PGY-100G-802.3_2015 is the instrument that enables the design and test engineers to test the 100G Ethernet interface for its BER by configuring PGY-100G as 100G 802.3 traffic generator with error injection and error correction capability in real time to validate the overall performance of interface.

Key Specifications

Specifications

Fixed Payload Patterns | Fixed Data Pattern |

Variable Payload Pattern | PRBS31; PRBS15; Incremental Pattern |

Interface | CFP (Two Ports) upgradable to 4 ports |