UFS 4.0 Protocol Analyzer

Product

Overview

Datasheet

Presentation

Application

Notes

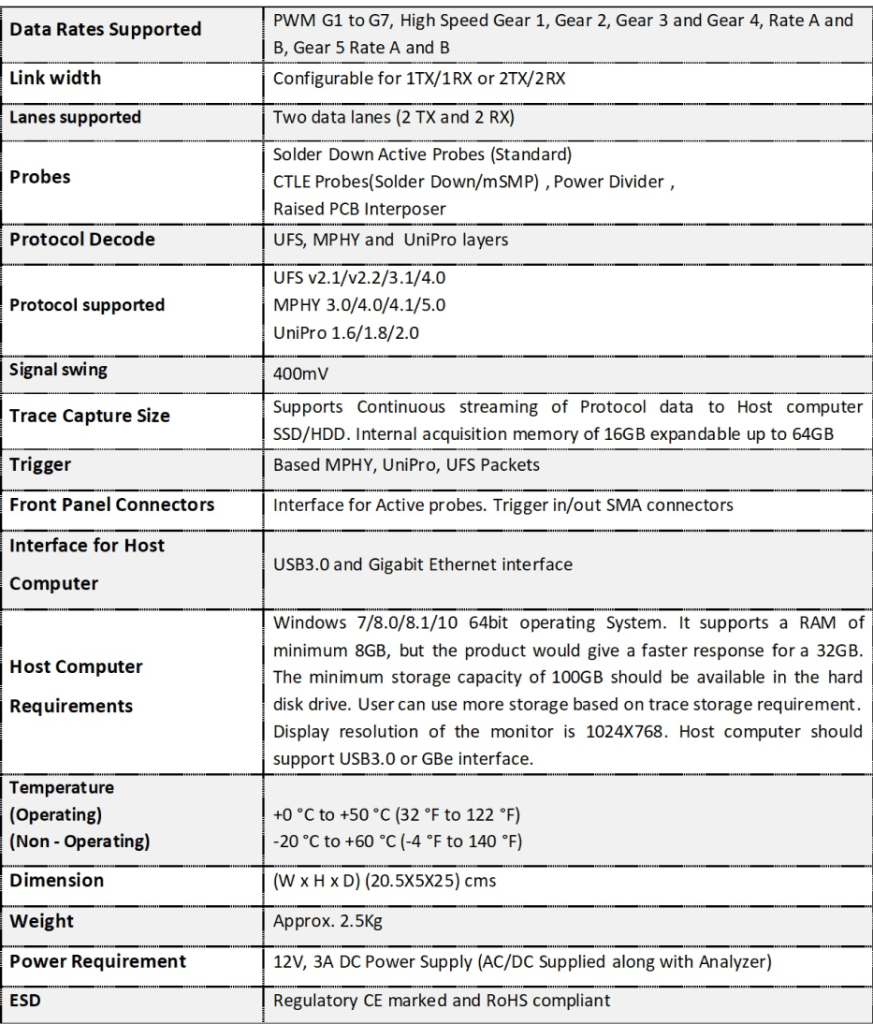

PGY-UFS4.0-PA, UFS Protocol Analyzer is the industry-first working and tested UFS4.0 Protocol Analyzer. It offers protocol data capture and debugging of data across MPHY, UniPro, and UFS protocol layers. It allows for instantaneous decoding of UFS, UniPro, and MPHY layers with the flexibility to correlate decoded data across these protocol layers. PGY-UFS4.0-PA supports PWMG1 to HSG5B data rates and two TX, and two RX lane decode. The active probe has minimum electrical loading on the device under test (DUT) and captures protocol data without affecting the performance of DUT. PGY-UFS4.0- PA Protocol Analyzer supports two-lane data. Comprehensive on the fly decoding of UniPro & UFS data enables validation of communication between UFS host and device.

PGY-UFS4.0-PA Protocol Analyzer allows Design and Test Engineers to obtain deep insight into UFS host and device communication. MPHY/UniPRO/UFS packet-based triggering allows specific protocol data capture and analysis. PGY-UFS Protocol analyzer instantaneously provides decoding of UFS, UniPro, and MPHY layers with a correlation to MPHY, UniPro, and UFS layers.

UART Protocol Exerciser and Analyzer Datasheet

Key features

- Supports custom UART traffic generation

- Simultaneously generate UART traffic and Protocol decode of the bus

- Variable UART baud rates

- Continuous streaming of protocol data to the host computer to provide a large buffer

- A timing diagram of Protocol decoded bus

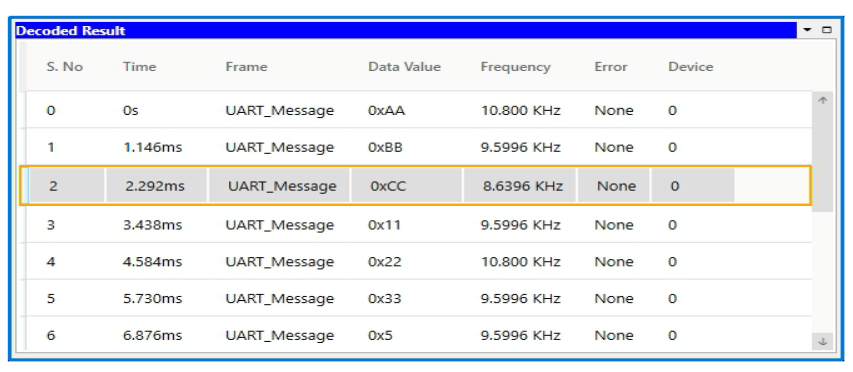

- Listing view of Protocol activity

- Error Analysis in Protocol Decode

- Ability to write exerciser script to combine multiple data frame generation at different data speeds

- USB 2.0/3.0 host computer interface

- API support for automation in Python or C++

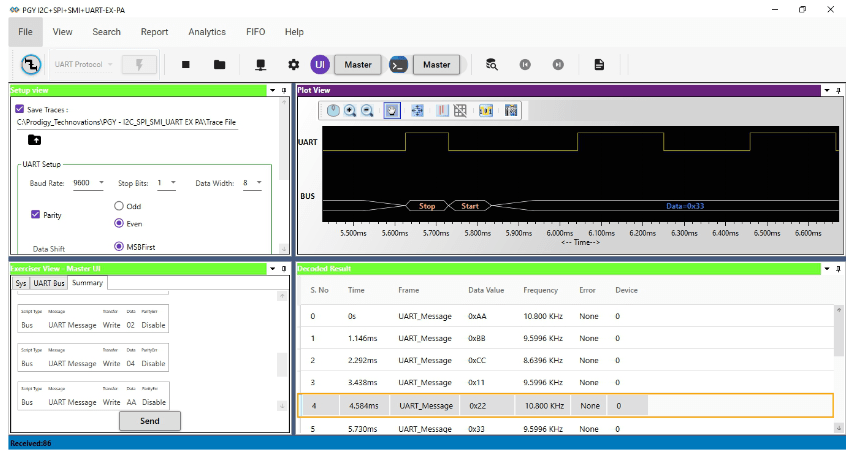

Multi-Domain view

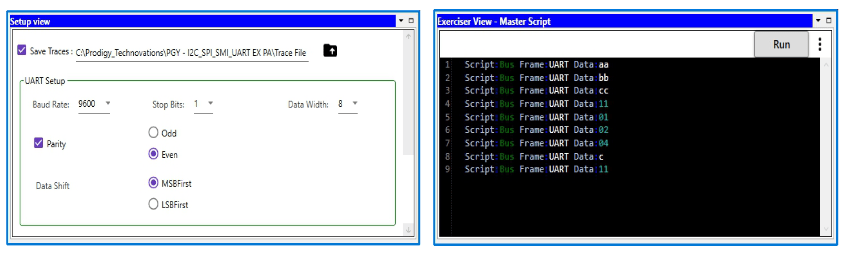

Exerciser

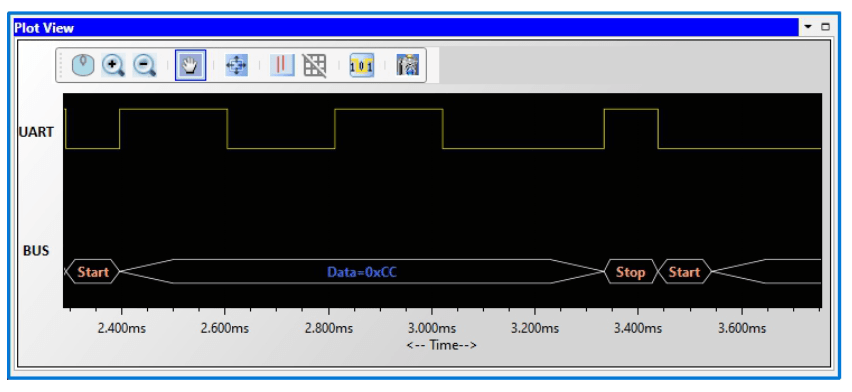

Timing Diagram and Protocol Listing View

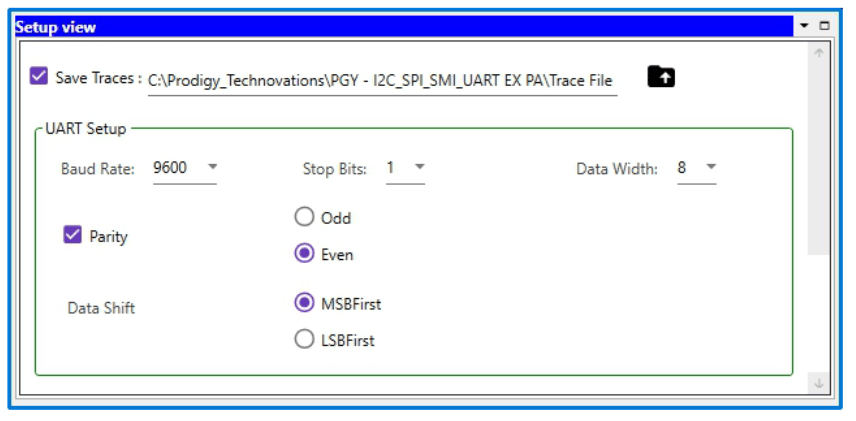

Setup View

Key Specifications

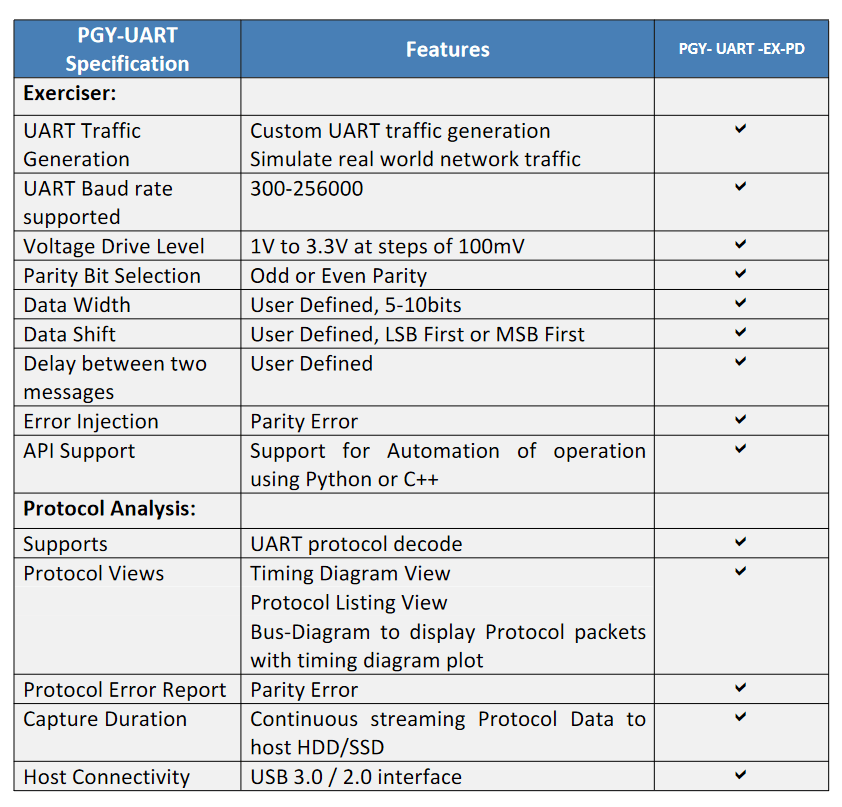

UART Specifications