# PGY-PCleGen3/4-PA

PCIe Protocol Analyzer (upto Gen 4 Datarates)

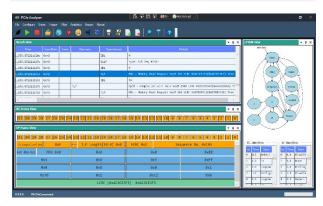

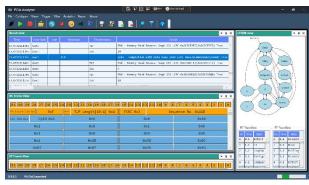

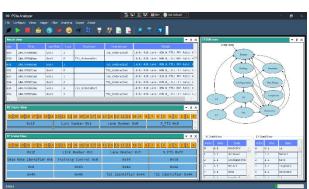

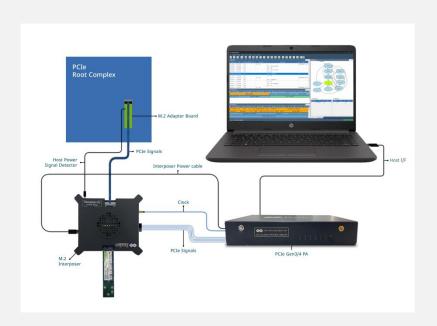

The PGY-PCIeGen3/4-PA is a PCIe Protocol Analyzer that supports protocol analysis up to PCIe Gen4 speeds. PCIe design and test engineers can easily captures and record traces at 2.5, 5.0, 8 and 16GT/s at specific event and obtain error report instantaneously at affordable price. This enables the design and test engineers to reduce the development time and address the time to market needs. PCIe Gen4 data is captured using interposers between the root complex and end point (Device under test). PCIe Gen4 interposers support. PCIe Gen4 Protocol Analyzer's software provides complete decode and error analysis of Transaction Layer Packets (TLPs), data link Layer Packets and with LTSSM information.

PGY-PCIeGen3/4-PA software provides powerful protocol decode capabilities enabling engineers to quickly identify the problems in protocol layer. Software is capable of decoding the packets and provide error analysis. Different views of Protocol layer enables the user to quickly identify the problems in protocol. Power search, filter-in, filter-out features simplify debug activity.

PGY-PCIeGen3/4-PA provides sophisticated protocol trigger features which allows trigger on specific protocol event and capturing the data of interest. Auto, simple and advanced trigger features capture PCIe bus activity, specific event and monitor multiple trigger conditions and capture data around it.

#### **Key features**

- PCIe Gen1/2/3/4-X4 Protocol Decode and Analysis.

- Currently supports four lane PCleGen1/2/3/4 Bus.

- Active M.2 Connector interposer for speeds up to PCIe Gen4 is standard offering with protocol analyzer.

- Optional Passive M.2 Connector interposer for speeds up to PCIe Gen3.

- Optional solder down probe tips for four lanes for speeds up to PCIe Gen3 (8Gbps)

- Protocol Decoding of TS1, TS2, TLP, DLLP Packets.

- Hardware based protocol packet TS1, TS2 and IDLE filter capabilities.

- Software based search, filter-in and filter-out capabilities.

- Hardware based protocol aware trigger capabilities.

- Advanced multi-level if-then-else if trigger capabilities.

- Standard buffer size of 16GB and expandable to 64GB combined for TX and RX.

- Trigger based on TS1, TS2, TLP and DLLP Packet content.

- Detailed view of each TLP/DLLP with all field values.

- LTSSM Analysis for PCIe protocol traffic.

- Memory segmentation with each segment with different trigger condition<sup>1</sup>.

- Trigger out signal at trigger event allows the triggering of other instruments such as an oscilloscope.

- Interface to host system using USB 3.0.

- Decoded data packets can be exported to .txt file for further analysis.

- PGY Protocol Analyzer is light weight and can be deployed for on-site/ field tests.

- Field upgradeable enables the unit to easy maintain for latest feature set.

|          |         |      | Lane |      |                |                                            |

|----------|---------|------|------|------|----------------|--------------------------------------------|

| 19076307 | 2.8925s | Gen3 | 2    |      | SKP_OrderedSet |                                            |

| 19076308 | 2.8925s | Gen3 | 3    |      | SKP_OrderedSet |                                            |

| 19076309 | 2.8925s | Gen3 |      |      | IDL            | 64                                         |

| 19076310 | 2.8925s | Gen3 |      |      |                | CfgNr0 - Configuration Write Type 0 Seq# 1 |

| 19076311 | 2.8925s | Gen3 |      | IDL  |                | 56                                         |

| 19076312 | 2.8925s | Gen3 |      |      | DLLP           | Type: Ack                                  |

| 19076313 | 2.8925s | Gen3 |      |      | IDL            | 48                                         |

| 19076314 | 2.8925s | Gen3 |      |      | TLP            | Cpl - Completion without Data Seg# 1       |

| 19076315 | 2.8925s | Gen3 |      |      | DLLP           | Type: UpdateFC-NP                          |

| 19076316 | 2.8925s | Gen3 |      |      | IDL            | 48                                         |

| 19076317 | 2.8925s | Gen3 |      |      | DLLP           | Type: Ack                                  |

| 19076318 | 2.8925s | Gen3 |      |      | IDL            | 48                                         |

| 19076319 | 2.8925s | Gen3 |      | DLLP |                | Type: Ack                                  |

| 19076320 | 2.8925s | Gen3 |      | IDL  |                | 56                                         |

| 19076321 | 2.8925s | Gen3 |      | DLLP |                | Type: UpdateFC-Cpl                         |

| 19076322 | 2.8925s | Gen3 |      | IDL  |                | 56                                         |

| 19076323 | 2.8925s | Gen3 |      | TLP  |                | CfgRd0 - Configuration Read Type 0 Seq# 2  |

| 19076324 | 2.8925s | Gen3 |      | IDL  |                | 76                                         |

| 19076325 | 2.8925s | Gen3 |      |      | TLP            | CplD - Completion with Data Seq# 2         |

| 19076326 | 2.8925s | Gen3 |      |      | DLLP           | Type: UpdateFC-NP                          |

| 19076327 | 2.8925s | Gen3 |      |      | IDL            | 48                                         |

| 10076210 | 2 9025# | Gon2 |      |      | DLLD           | Type: Ack                                  |

| Specifications                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Data Rates Supported          | PCIe Gen1, Gen2, Gen 3, Gen 4. ( with Option PCIe4)                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Link Width                    | Four lanes (Four TX and Four RX).                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Probes                        | Active M.2 Interposer (Standard) Solder Down Active Probes for speeds up to PCIe Gen3. (Optional)                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Protocol Decode               | TS1, TS2, TLP, DLLP,SDS, IDLE, EIOS, EIEOS, FTS, SKP                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Trace Capture Size            | Supports Continuous streaming of Protocol data to Host computer SSD/HDD. And Post Capture up to buffer size.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Trigger                       | Based on TS1, TS2, TLP, DLLP.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Connectors                    | Interface for Active probes. Trigger in/out SMA connectors.                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Interface for Host Computer   | USB 3.0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Host Computer<br>Requirements | Processor: Intel i7 10 <sup>th</sup> Generation or better (Equivalent) Operating System: Windows 7/8.0/8.1/10 64bit OS.  RAM: minimum 16GB but the product would give a faster response for 32GB/64GB/more.  Storage: 256GB SSD or more (minimum storage capacity of 1GB should be available in the hard disk drive. User can use more storage based on trace storage requirement.)  Display resolution: 1024X768.  Interface: Host computer should support USB 3.0 interface. |  |  |  |  |  |  |

| Dimension (W x H x D)         | (W x H x D) (20.5X5X25) cms.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| Weight                        | Approx. 4 kg.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| Power Requirement             | 12V, 6A DC Power Supply (AC/DC Supplied along with Analyzer).                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

# **Prodigy Interposers**

• Prodigy M.2 Interposer (PGY-INT-M.2)

M.2 Interposer connection setup

Prodigy SD Express Interposer (PGY-INT-SDX)

SD Express Interposer connection setup

### **Ordering information:**

PGY-PCIeGen3/4-PA: PCIe Gen3/4 Protocol Analyzer

**Note:** Unit by default supports up to Gen 3 data rates. For Gen4 support, please include Opt PCle4 at time of ordering.

(Shipment includes Hardware, software CD, One Active M.2 Interposer, USB 3.0 Cable and Power adapter)

**Opt PCIe4**: Add PCIeGen4 support PGY-INT-M.2: Prodigy M.2 Interposer

PGY-INT-SDX: Prodigy SD Express Interposer

Post Purchase Upgrade:

PGY-UPG-Gen3/4 Upgrade to PCleGen 4 from PCleGen3

#### **Warranty:**

12 Months of Hardware Warranty & Software upgrade Support

(Accessories, Interposer, Probes are covered for a 90 Days warranty only against any manufacturing defects)

## **About Prodigy Technovations Pvt Ltd**

**Prodigy Technovations** is the leading provider of innovative protocol analysis solutions for mainstream and emerging technologies. We provide Protocol Decode, and PHY layer testing solutions on Test & Measurements equipment's. The company's ongoing efforts include successful implementation of innovative and comprehensive protocol Analysis solutions using latest hardware technologies.