DDR5 is fifth generation dynamic random-access memory provides superior performance over DDR4. It is designed for next generation CPUs and GPU to address artificial intelligence applications and large data...

Introduction The MIPI I3C Bus interface enhances the legacy I2C standard by reducing the number of physical pins required in sensor systems while supporting low-power, high-speed digital communication, similar...

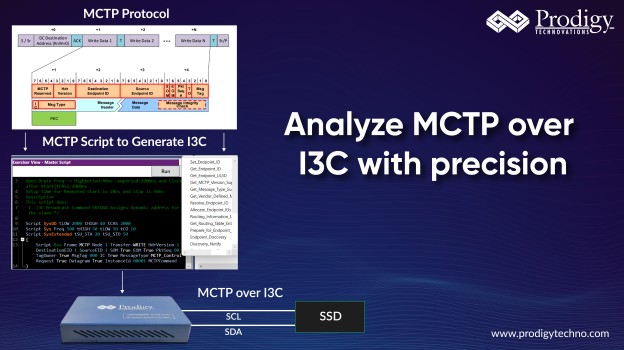

MCTP Over I3C in the PGY-I3C-EX-PD Overview of I3C MIPI I3C, or I3C, stands for the MIPI I3C (Sensor Interface) standard, which serves as a versatile and efficient interface...

Timing Challenges in I3C Protocol Communication Conquering the Timing Challenges in I3C communication with Prodigy’s Solutions! One of the primary challenges in designing I3C Protocol communication is the occurrence of timing issues,...

Next-Gen Sensor Challenges Sensor Challenges in Next Generation Consumer Devices, IOT, and Automotive Design. Over the last decade, we have seen an explosion of mobile phone devices along with...

I3C Protocol: Understanding and Debug What is MIPI I3C? The MIPI I3C Bus interface is an evolutionary specification that builds upon the legacy I2C standard. The aim is to...

I3C vs I2C Protocol Analyzer What is I2C Protocol? I2C stands for Inter IC communication. I2C Protocol is a simple two-wire protocol used to communicate between two devices or...

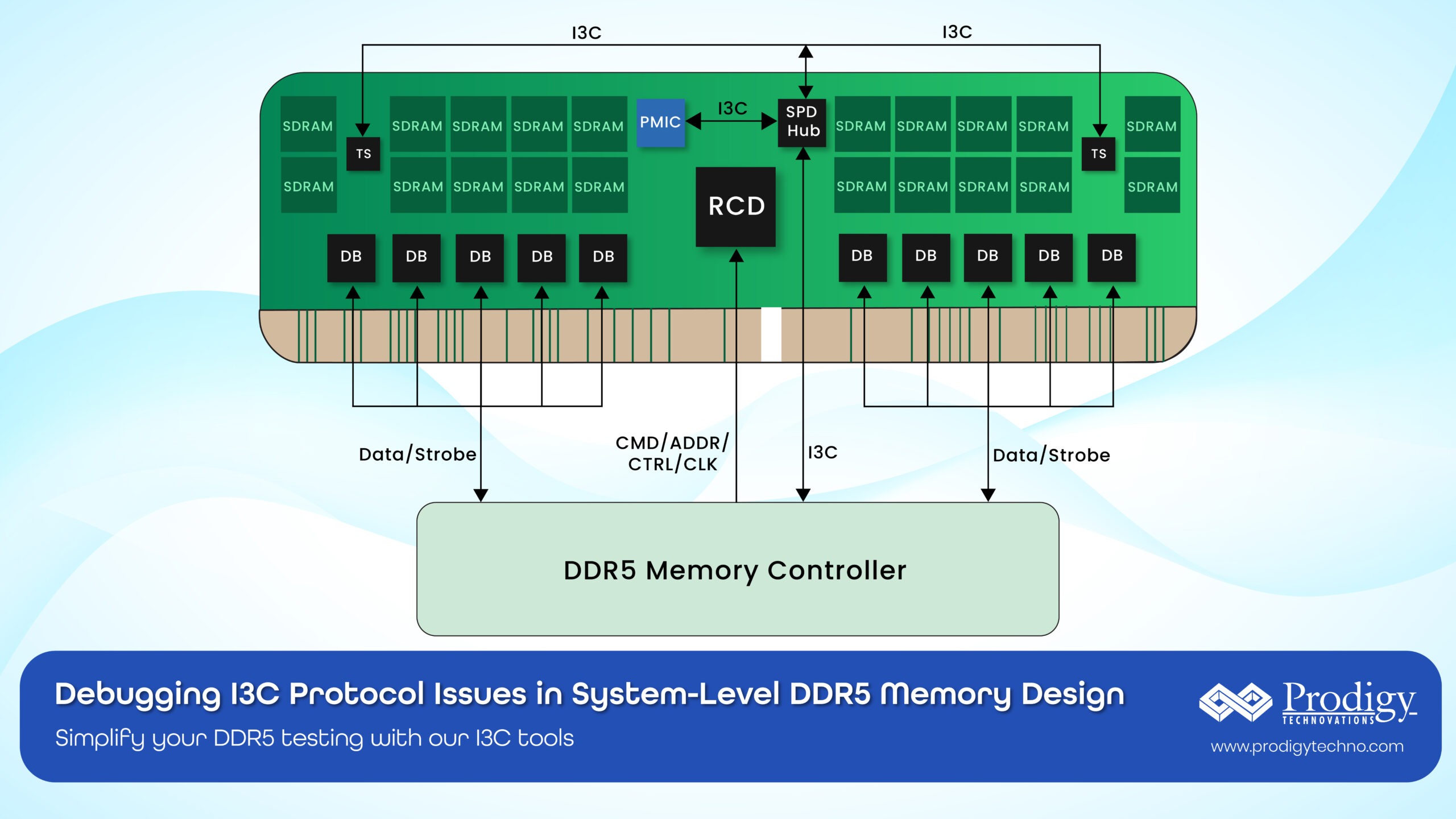

DDR5 I3C What is the role of the I3C Protocol in DDR5? DDR5 has significant improvement over DDR4. DDR5 offers higher bandwidth with a data rate of up to...

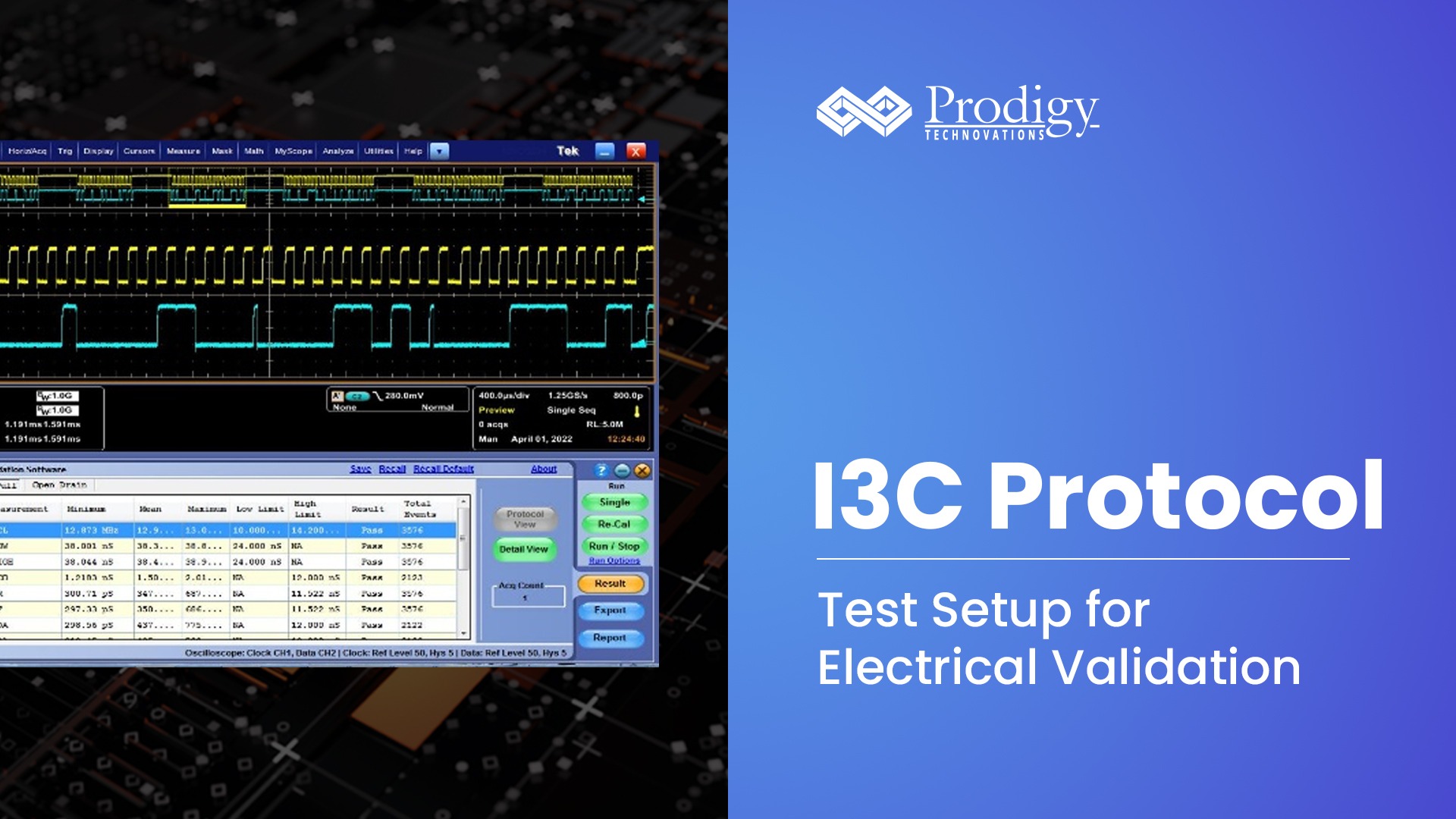

I3C Protocol: Test Setup for Electrical Validation I3C devices are going through mass adoption at the moment. One challenge however remains for I3C devices is interoperability. The I3C devices...

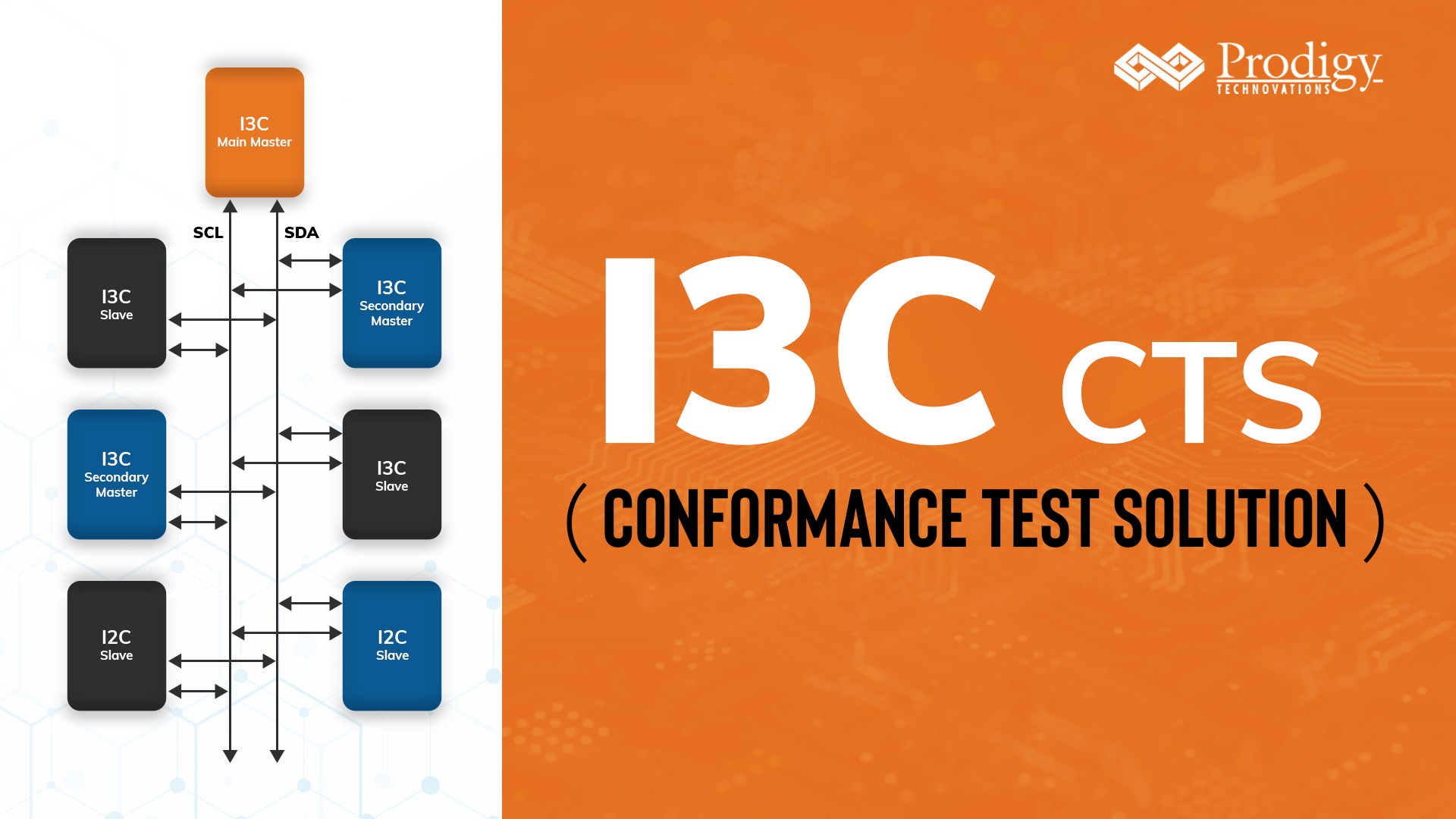

I3C CTS (Conformance Testing Suite) How to test the I3C devices for Interoperability or Conformance Testing? I3C Protocol is gaining momentum and going to be mainstream technology in automotive,...