Overview

In the realm of embedded systems, I2C (Inter-Integrated Circuit) is a widely used communication protocol that enables devices to communicate with each other over a short distance. One critical aspect of I2C communication is clock stretching, which allows slower devices to control the pace of communication by holding the clock line low. One of the challenge for design engineer to monitor the infrequent clock stretching event while multiple I2C connected in the bus. Which device is stretching the clock and how it is affecting the performance of the embedded system.

The PGY-LA-EMBD, a high-performance logic analyzer, offers advanced features for analyzing I2C signals, including pulse width triggering of clock stretching. This document provides an overview of how pulse width triggering on clock stretching can be achieved using the PGY-LA-EMBD logic analyzer.

Clock Stretching in I2C

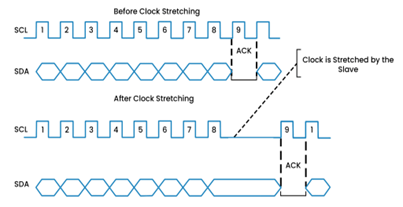

Clock stretching is a mechanism used in I2C communication where a slave device can hold the SCL (clock line) low to signal the master to wait before continuing communication (as illustrated in Figure1). This ensures data integrity when the slave needs more time to process information. The master device must wait until the slave releases the SCL line before resuming communication. This feature is particularly useful when the slave requires extra time for processing, buffering, or synchronization, but it does require the master to support clock stretching for the communication to proceed correctly.

Figure 1: I2C Clock Stretching

Pulse Width Triggering

Pulse width triggering is a powerful feature in logic analysers that allows users to capture events based on the duration of a pulse. In the context of I2C clock stretching, this feature is particularly useful for detecting and analysing instances where the clock line (SCL) is held low for clock stretching to by the device in a i2C since this device needs more time to respond. In an I2C bus, not all devices will equal response time. Though I2C bus may work 10Kbps speed, to capture infrequent event of clock stretching in an logic analyser or I2C analyser is difficult. The pulse width triggering enables the capturing of this event by setting pulse width trigger by setting pulse width more than 100Kbps data rate. This capability helps engineers identify timing issues, performance bottlenecks, and other anomalies in I2C communication.

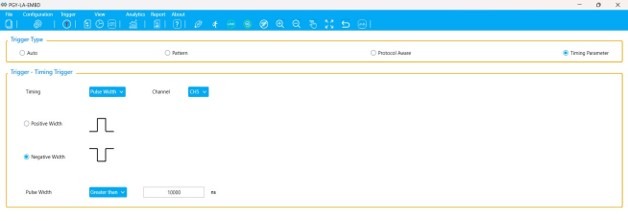

The PGY-LA-EMBD offers various triggering options, including pattern triggers, protocol-aware triggers, and timing parameter triggers. The timing parameter trigger, a form of pulse width triggering, allows users to set the pulse width on the negative edge. This means the PGY-LA-EMBD will trigger on the negative edge if the clock line stays low longer than the specified pulse width.

Figure 2: Pulse width trigger setting on PGY-LA-EMBD

For example, in Figure 2, the pulse width triggering is configured with a pulse width greater than 10,000 ns on the negative edge. In this example, the I2C signal is captured with a frequency of 100 kHz and a period of 10,000 ns. At some instances, clock stretching occurs, and the pulse width triggering feature in the PGY-LA-EMBD is used to capture these events accurately.

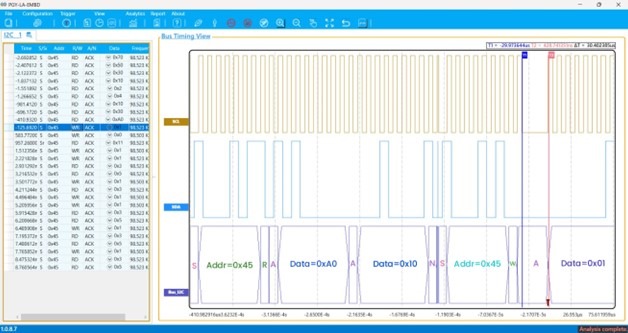

Figure 3: waveform captured for I2C Clock stretching

Figure 3 illustrates an I2C waveform during a write-read transmission. After the read transmission, the clock is stretched during the write message, resulting in a clock stretching event lasting 30,000 ns. Vertical cursors are used to measure the duration of this clock stretching. Clock stretching occurs when the I2C slave device holds the clock line (SCL) low, temporarily pausing communication to process data. In this example, the PGY-LA-EMBD logic analyzer is configured to trigger on clock stretches longer than 10,000 ns to capture this infrequent event. When this threshold is exceeded, logic analyzer with I2C decoding capability will notify the trigger point is marked with a “T” on the bus view, making it easy to identify and analyse the delay. This setup helps diagnose timing and performance issues in I2C communication, ensuring reliable operation.

Conclusion

Pulse width triggering of clock stretching on I2C using the PGY-LA-EMBD logic analyzer with I2C decoding capability provides a robust method for analysing and troubleshooting I2C communication. By leveraging the advanced triggering capabilities of the PGY-LA-EMBD, engineers can gain deeper insights into the timing behaviour of their I2C systems, ensuring reliable and efficient communication in their embedded applications.